74AC11194

74AC11194 is 4-BIT BIDIRECTIONAL UNIVERSAL SHIFT REGISTER manufactured by Texas Instruments.

74AC11194 4- BIT BIDIRECTIONAL UNIVERSAL SHIFT REGISTER

- Parallel-to-Serial, Serial-to-Parallel

Conversions

- Left or Right Shifts

- Parallel Synchronous Loading

- Direct Overriding Clear

- Temporary Data Latching Capability

- Flow-Through Architecture to Optimize

PCB Layout

- Center-Pin VCC and GND Configurations to

Minimize High-Speed Switching Noise t- EPIC (Enhanced-Performance Implanted CMOS) 1-mm Process

- 500-m A Typical Latch-Up Immunity at

125°C

- Package Options Include Plastic

Small-Outline Packages, and Standard

Plastic 300-mil DIPs

SCAS093

- NOVEMBER 1989

- REVISED APRIL 1993

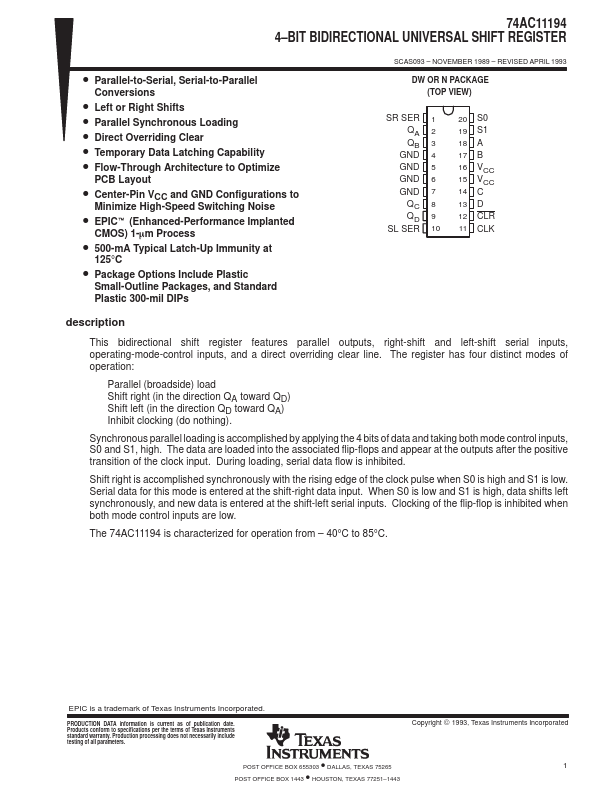

DW OR N PACKAGE (TOP VIEW)

SR SER

QA QB GND

QC QD SL SER

1 2 3 4 5 6 7 8 9 10

20 S0 19 S1 18 A 17 B 16 VCC 15 VCC 14 C 13 D 12 CLR 11 CLK description

This bidirectional shift register Features parallel outputs, right-shift and left-shift serial inputs, operating-mode-control inputs, and a direct overriding clear line. The register has four distinct modes of operation:

Parallel (broadside) load Shift right (in the direction QA toward QD) Shift left (in the direction QD toward QA) Inhibit clocking (do nothing).

Synchronous parallel loading is acplished by applying the 4 bits of data and taking both mode control inputs, S0 and S1, high. The data are loaded into the associated flip-flops and appear at the outputs after the positive transition of the clock input. During loading, serial data flow is inhibited.

Shift right is acplished synchronously with the rising edge of the clock pulse when S0 is high and S1 is low. Serial data for this mode is entered at the shift-right data input. When S0 is low and S1 is high, data shifts left synchronously, and new data is entered at the shift-left serial inputs. Clocking of the flip-flop is inhibited when both mode control inputs are low.

The 74AC11194 is characterized for operation...